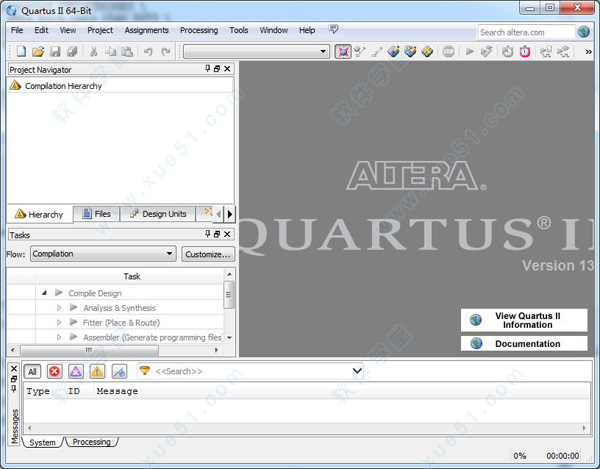

quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]

quartus ii 13是Altera公司开发的一款专注于FPGA、CPLD以及结构化ASIC设计的开发软件。它分享完全集成且与电路结构无关的开发包环境,且具有数字逻辑设计的全部特性,具有原理图、VHDL、VerilogHDL以及AHDL等多种设计输入形式,且内嵌有综合器以及仿真器,能够帮助用户完成从设计输入到硬件配置的完整PLD设计流程。且软件界面功能分布明确,整个软件也是易学易懂,知识兔为大家分享的还是quartus ii 13.0破解版,且32和64位版本度支持,有需要的朋友可以来下载体验哦,知识兔小编为大家附上了安装破解教程!

安装教程

1、在知识兔的百度网盘资源上下载好软件安装包,将其解压好,然后知识兔知识兔双击运行里面的“QuartusSetup-13.0.0.156.exe”安装程序,连续知识兔点击“next”对软件进行安装。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/20180328152141820.jpg)

2、建议不要修改软件的安装目录,由于后面破解软件的时候需要到软件的安装目录下。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281521455332.jpg)

3、安装时间也是比较长的,请耐心等待。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281521506503.jpg)

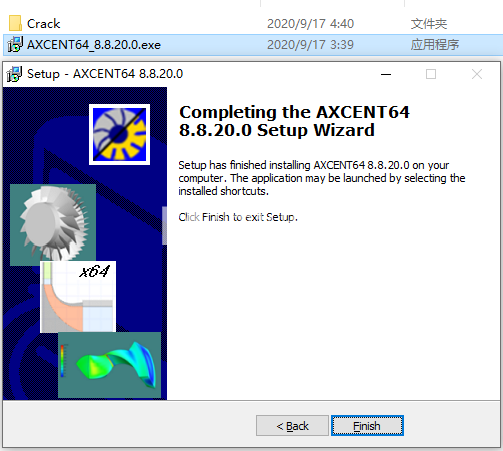

4、软件安装完成,知识兔点击“finish”。若软件自动打开了,请直接将其关闭。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281521548360.jpg)

破解教程

1、安装完成软件之后选择对应你电脑位数的破解器,然后知识兔知识兔双击运行,先知识兔点击“应用”,提示“搜索文件”,知识兔点击“是”。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281522044993.jpg)

2、然后知识兔去到安装目录:C:altera13.0quartusbin64下,知识兔选择“sys_cpt.dll”,知识兔点击“打开”。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/2018032815220738.jpg)

3、此时会在软件的安装目录下回生成一个“license”文件,提示另存,直接知识兔点击“保存”即可。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281522106093.jpg)

4、最后破解器会显示破解文件到处完成,直接退出。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/20180328152213514.jpg)

5、然后知识兔知识兔双击运行软件在桌面上的快捷方式,知识兔打开软件,弹出提示,知识兔选择第二个选项。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281522179551.jpg)

6、进入到软件后,弹出提示,知识兔点击“yes”即可。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281522221509.jpg)

7、在软件的导航栏,知识兔点击“tools”—“license setup”。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281522269300.jpg)

8、在弹出来的窗口上复制下方的“ID”。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281522302638.jpg)

9、然后知识兔去到软件的按住那个目录下:C:altera13.0quartusbin64,找到之前生成的license文件“license.dat”,然后知识兔用记事本打开它。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281522342463.jpg)

10、知识兔将图中被框中的“XXXXXXXXXX”,全部替换为之前复制的“ID”,然后知识兔保存,这样即可成功破解。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281522404972.jpg)

使用教程

一、新建工程,写代码

1、创建工程文件夹

在电脑上新建一个文件夹,例如E:Lianxi_1。工程的文件将全都存在这个文件夹内,便于管理。一个工程对应一个文件夹。

2、新建工程

打开QuartusII,File->New Project Wizard…如下图:

第1个,知识兔选择工作目录:选刚才建立的空文件夹.

第2个,填入工程名称。要有意义,比如要做一个38译码器,工程名就叫decoder3_8,不要使用中文。

第3个,顶层设计实体名,默认。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281523002764.jpg)

↓

Next… 下图,添加已有的源代码文件,没有的话,点Next![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281523072943.jpg)

↓

下图,选FPGA型号,知识兔根据你FPGA芯片上印刷的型号选择。

比如,我使用的芯片型号如下:

Family: Cyclone II

Device:EP2C5T144C8![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281523167054.jpg)

↓

Next…下图,知识兔选择综合、仿真、时序分析工具. 此处如果知识兔全部选择None,表示用Quartus自带的工具。

注:Quartus 9.1以后的版本不再自带仿真工具,需要安装Modelsim之类的软件来仿真。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281523209534.jpg)

↓

Next.. 下图,是前面设置的信息的总览,检查无误就点Finish![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281523231923.jpg)

2、写代码![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281523266506.jpg)

↑

新建VerilogHDL文件,写代码,保存时,文件名要与module后面定义的实体名一致。即,保存decoder3_8.v到你的工程文件夹内。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281523296004.jpg)

保存为 decoder3_8.v

将此源文件设置为顶层文件,如下图:

导航窗口Project Navigator下边→点Files

右击文件decoder3_8.v

设为顶层实体Set Top-Level Entity![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281523334490.jpg)

![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281523371036.jpg)

再知识兔点击工程架构Hierachy,检查顶层架构是否为当前顶层文件。

说明:一个工程内,知识兔可以有多个源代码文件。但只有一个是顶层文件,代表最顶层设计,它可以引用工程目录内的其他源文件。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281523413290.jpg)

二、编译工程,找错误

编译:Processing–>Start Compilation

编译不成功时,下方会有红色提示信息,请仔细检查语法,知识兔双击红色提示信息,知识兔可以直接定位到错误代码附近位置。

修改后重新编译,直至修改完所有错误。

编译成功,只是语法没有错误,但并不代表设计就是完全正确的。

知识兔可以通过仿真来检查设计是否符合预计的功能。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281523568501.jpg)

三、分配引脚,重编译

前面的设计完成后,开始分配引脚

说明:FPGA引脚众多,大部分引脚都可以任意设置为输入或输出,知识兔可以将本工程中输入输出分配到任意可分配的引脚上。当然,对于已经做好的硬件开发版来说,有些按键、显示灯等已经事先与FPGA连接好了,所以分配引脚的时候要根据硬件电路原理图正确分配引脚。

分配引脚操作:Assignment -> Pin Planner,如图。分配完引脚,关闭窗口,重新编译工程。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281524047923.jpg)

四、知识兔下载配置,到硬件

下载程序到FPGA,有多种方式,知识兔一般用USB-Blaster。![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281524119349.jpg)

1、连接下载器

? 将USB-Blaster的USB端插电脑上,另一端10针接头接FPGA板上的JTAG插座。

? 用一根USB线给FPGA板供电。

如果知识兔你的电脑第一次使用USB-Blaster下载器,需要为它安装驱动:

方法:我的电脑右键->设备管理器->USB-Blaster右键->更新驱动->定位到Quartus安装目录C:altera9.0quartusdriversusb-blaster,等待安装完成

2、知识兔下载

菜单Tools -> Programmer,下图![quartus ii 13.0 64/32位破解版下载(附安装教程)[百度网盘资源]](https://www.xue51.com/uppic/180328/201803281524146263.jpg)

左上方,点Hardware Setup…->下拉选择USBBlaster->Close;

界面顶部中间选下载方式,Mode: JTAG

左侧,按Start下载 .sof文件。

OK,测试硬件功能是否正确吧。

功能介绍

1、自动定位编译错误;

2、高效的期间编程与验证工具;

3、功能强大的逻辑综合工具;

4、芯片(电路)平面布局连线编辑;

5、定时/时序分析与关键路径延时分析;

6、完备的电路功能仿真与时序逻辑仿真工具;

7、使用组合编译方式可一次完成整体设计流程;

8、可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析;

9、能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件;

10、quartus ii 13.0破解版支持软件源文件的添加和创建,并将它们链接起来生成编程文件。

11、Quartus II分享了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,知识兔包括:

12、可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;

13、LogicLock增量设计方法,用户可建立并优化系统,然后知识兔添加对原始系统的性能影响较小或无影响的后续模块;

增强功能

高级设计流程

1、OpenCL的SDK为没有FPGA设计经验的软件编程人员打开了强大的并行FPGA加速设计新世界。

从代码到硬件实现,OpenCL并行编程模型分享了最快的方法。与其他硬件体系结构相比, FPGA的软件编程人员以极低的功耗实现了很高的性能。

2、Qsys系统集成工具分享?曰贏RM的Cyclone V SoC的扩展支持。

现在,Qsys可以在FPGA架构中生成业界标准AMBA AHB和APB总线接口。而且知识兔,这些接口符合ARM的TrustZone要求,知识兔支持客户在安全的关键系统资源和其他非安全系统资源之间划分整个基于SoC-FPGA的系统。

3、DSP Builder设计工具支持系统开发人员在DSP设计中高效的实现高性能定点和浮点算法。

新特性包括更多的math.h函数,提高了精度,增强了取整参数,为定点和浮点FFT分享可参数赋值的FFT模块,还有更高效的折叠功能,提高了资源共享能力。

常见问题

问题一:

USB Blaster连接上,电脑无任何反应,之前安装过驱动也能使用,于是卸载Quartus并重装,问题解决。

问题二:

在综合时,出现错误,说软件不支持全部的器件,明显是破解不完全。原来是破解步骤有误,做了修正。

问题三:

能下载程序,但是程序不工作,很可能是晶振的问题(晶振不接也可以正常下载程序的),知识兔以为是晶振虚焊什么的,最后发现是晶振引脚与芯片时钟之间一个电阻未连接。

特别说明

提取码:63ch 提示:该资源为网盘资源,请提前安装好百度网盘。

下载仅供下载体验和测试学习,不得商用和正当使用。