quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]

quartus ii 11是一款非常强悍的FPGA、CPLD以及结构化ASIC设计软件,它的性能效能可以说在行业是都是首屈一指的。它能够为用户分享完善的timing closure和LogicLock基于块的设计流程以及FPGA和固定功能HardCopy器件统一设计流程的设计工具,使得的设计概功能更加的强大,再加上它本身使用的金蛋性,操作的易学行,使得他更加的受用户的欢迎。知识兔分享quartus ii 11.0破解版下载,无需注册码破解,附有quartus ii11.0破解器,且知识兔小编还为大家附上了安装破解使用教程!![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/201803291658042013.jpg)

安装教程

1、在知识兔的百度网盘资源上下载好软件安装包,将其解压好后,知识兔双击运行里面的“11.0_quartus_windows.exe”安装程序,解压数据,知识兔点击“install”。![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/201803291658334008.jpg)

2、然后知识兔连续知识兔点击“next”,一切默认就好,由于软件本身比较大,大壮需要一段时间,请耐心等待。![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/201803291658366396.jpg)

3、安装完成,知识兔点击“finish”。![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/201803291658381574.jpg)

4、软件会自动打开的话,直接关闭就好

破解教程

1、知识兔将安装包内的“Quartus_11.0_x86破解器(内部版).exe”破解器复制到软件的安装目录下,然后知识兔知识兔双击打开它,知识兔点击“应用”。![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/201803291658461620.jpg)

2、生成一个“license.dat”文件,默认保存在软件的安装目录下,知识兔点击“保存”。![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/201803291658502067.jpg)

3、然后知识兔破解器会提示运行完毕,直接退出即可。![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/201803291658538980.jpg)

4、然后知识兔知识兔双击软件在桌面上的快捷方式打开软件,提示需要有许可证,知识兔是没有的,直接选择默认的第一个,进入到软件。![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/201803291658554484.jpg)

5、然后知识兔知识兔点击“tool”—“license setup”。![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/201803291658596964.jpg)

6、会弹出一个界面,复制下面的“ID”号,然后知识兔关闭软件。![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/201803291659033581.jpg)

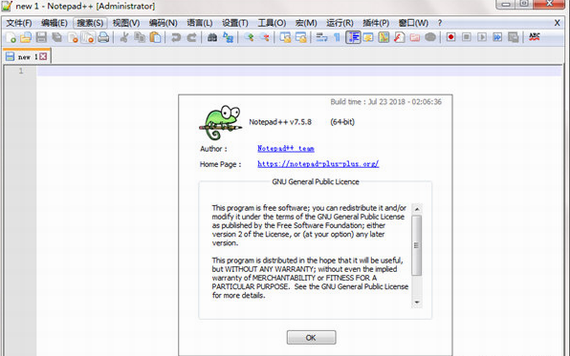

7、去到软件的安装目录下,找到“license.dat”文件,知识兔以记事本的方式打开软件,将里面的“XXXXXXXXXX”全部替换成你之前复制的“ID”号,然后知识兔保存,即可破解完成。![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/201803291659061373.jpg)

8、然后知识兔再次知识兔双击软件,就不会提示需要许可证之类?牧耍憔涂梢杂谰妹夥咽褂谩皅uartus ii 11.0破解版”了。![quartus ii 11.0破解版免注册码下载(附安装破解使用教程)[百度网盘资源]](https://www.xue51.com/uppic/180329/20180329165909779.jpg)

quartus11.0使用教程

一、设计流程:设计输入,综合适配,仿真下载。

编译器:原理图设计输入,文本编辑AHDL,VHDL,Verilog。内存编辑Hex,Mif。

要这道文件的格式代表的意义:

有quartus:Verilog 的拓展名:.v ;VHDL的拓展名:.vhd ;AHDL的拓展名:.tdf ;

原理图的拓展名:.bsf ,gdf;

利用quartus软件设计的流程是:设计输入(可以是程序文件,知识兔也可以是原理图文件)—》分析与综合(这个功能的分析)——》综合布线——–》时序分析(时序分析)——-》引脚的锁定及下载

1、设计输入:VHDL语言描述在状态机,控制逻辑,总线功能方面较强;而原理图输入顶层设计,数据通路逻辑方面有图形化强,功能明确的特点

2、综合和分析:先进行语法的分析和校正,依据逻辑设计描述和各种约束条件进行编译,优化,转化和综合。最终获得门级电路甚至更底层的电路描述网表文件

3、仿真:包括了功能仿真和时序仿真。功能仿真是直接对VHDL,原理图描述的逻辑功能进行测试,看是否满足了功能要求,不涉及具体器件的硬件特性。时序仿真:接近真实器件特性的仿真,仿真精度高。Quartus可以通过建立和编辑波形文件,来执行模拟分析。

4、布局布线:目的是将综合后产生的网表文件配置与指定的器件中,使之产生最终的下载文件

5、时序分析;分析逻辑的性能,协助时序分析,验证驱动芯片外信号的时钟至管脚延时

6、引脚锁定及下载:硬件的测试,将输入输出信号锁定在引脚上,通过编程电缆向CPLD进行下载

二、VHDL输入的流程

新建工程--》新建VHDL文件--》功能仿真--》全编译--》时序仿真--》引脚锁定和下载。

1:File->New Project Wizard–》填写项目路径和名称–》是否向工程添加文件–》选择目标芯片系类(可以再Assignments—>Divices中调出)—》选择是否用第三方的EDA工具

2:File–>New—>VHDL File—->编写文件(可以再导航栏中右击顶层实体—》setting—》添加文件;可以再Assignments—>Setting—-》添加文件)—-》保存

3:分析和综合Processing—》start—-》Start Analysis&Synthesis(快捷按钮)

在这一步中可能会出现top-level design entity is undefined,最起码我的在这个上面出现了几次的错误,顶层实体的错误:可以首先在Assignments–>Setting—>General中看看实体的名字是否是正确的。如果知识兔是搜的别人的代码一定要看看代码的内容其中

entity forth is

generic(LEN : integer :=2);

port(

clkin : in std_logic;

clkout : out std_logic

);

end forth;

这个是一个实体的定义。在开始和结束的时候一定要保证实体的名字和文件名字一样和工程的名字也是一样的。

4:指定仿真模式:由于在quartus11.0 当中的模拟工具和软件是分离的(在quartus中找不到simulator,也没有波形文件),因此要借助?谌降姆抡婺D狻R〉玫谌降闹С郑已∪〉氖荕odelsim10.1a,这里安装的版本不一样在quartus中的设置是不一样的。

在Assignments—-》Setting—–》EDA Tool setting—–》Simulation中选择Tool name 为Modelsim

在Tool—->option——》EDA tool option 中——》Modelsim的路径要把安装的Modelsim中安装文件的D:\modelsim\win32目录填写

在Assignments —->Simulation—-》more EDA Netlist Writer Settings——-》Compile test bench选取在项目用VHDL文件

仿真的动作是在Tools—>run EDA simulation tool—> EDA RTL simulation

5:全编译

在确定了工程选定的芯片(Assignments—-》Device中查看)

选择配置失败后重新启动(这个是默认选项,不用修改)

如果知识兔要将配置文件下载到配置器件中(Assignments—-》Device—》Device and pin option—->Configuaration;一般是默认配置的)

全编译—》Processing—-start- Compilation,编译后课查看报告

6:时序仿真:

建立波形仿真

7引脚锁定和下载

引脚锁定,在芯片的特定的引脚将文件中的内容输入和输出?

Assignments—-》Assignment editor ?在To和From中确定引脚

保存引脚信息,做一次全编译,知识兔以便将锁定信息编译进下载文件

下载,将编译生成的sof文件下载到FPGA中 Tool—-》programmer

三、全局优化

在assignment/settings/,physical synthesis optimization中,有几个?∠?:

1、optimize for performance(性能优化)

perform physical synthesis for combinational logic 对组合逻辑进行优化

perform register retiming ?对寄存器进行优化

2、effort level ?级别

相应的不同的级别的不同之处在后面的解释中说明,主要体现在了编译时间的多少,当然与提高的性能之间呈反比的关系

3、fitter netlist optimization ? 布局布线网表优化

第一个选项是对异步信号自动的添加流水线

第二个选项执行寄存器的复用

4、optimize for fitting 布局布线的优化

第一个选项是针对组合逻辑电路而言

第二个选项 对逻辑和寄存器进行优化

新功能

1、软件支持MAX7000/MAX3000等乘积项器件

quartus ii 11.0设计软件现在除了支持Altera的APEX 20KE,APEX 20KC, APEX II,ARM的Excalibur嵌入处理器方案,Mercury,FLEX10KE和ACEX1K之外,知识兔还支持MAX3000A,MAX7000系列乘积项器件。MAX3000A和MAX7000设计者现在可 以使用QuartusII设计软件中才有的所有强大的功能

2、软件体积缩小,运行速度加快

安装软件为290M,完全安装为700M,如果知识兔定制安装,不选择Excalibur嵌入处理器,则安装所需空间为 460M,比QuartusII1.1版本减少一半以上的空间要求,却能支持ALTERA全部芯片的开发。同时软件的装载,编译,仿真速度比1.1版本大 大加快

3、LogicLock设计流程把性能提升15%

quartus ii 11.0设计软件通过增强层次LogicLock模块级设计方式,将性能平均改善15%。LogicLock设计流程把整个模块的放?媒挥缮杓普呖刂疲绻匾幕埃梢圆捎酶ㄖ矫娌贾谩ogicLock设计流程运行设计者单独地优化和锁定每个模块的性能,在大型SOPC设计的构建过程中也保持整个系统的性能。2.0版Quartus II设计软件把新的LogicLock设计流程算法集成到未来的Altera器 件中,该算法充分利用了模块级设计的优势

4、采用快速适配选项缩短编译时间

增加了一个新的快速适配编译选项,知识兔选择中这个选项,将会比缺省设置要缩短50%的编译时间。快速适配功能保留了 最佳性能的设置,加快了编译过程。这样布局适配算法反复的次数更少,编译速度更快,对设计性能的影响最小

5、新的功能减小了系统级验证

设计软件引入了新的功能,加快验证过程,这通常是SOPC设计流程中最漫长的阶段。在最初的编译时间中,新的SignalProbe技术允许用 户在保留设计最初布线,时限和设计文件的同时把内部节点引到未用的管脚进行分析。SignalProbe技术完成了现有SignalTap嵌入逻辑分析的功能。而且知识兔设计者能够使用新版本中分享的HDL测试模板快速地开发HDL仿真矢量

软件特点

1、Quartus II设计软件也可以自动地从QuartusII仿真器波形文件中创建完整的HDL测试平台

2、破解版支持高速I/O设计,生成专用I/O缓冲信息规范(IBIS)模型导入到常用的EDA信号集成工具中。IBIS模型根据设计中每个管脚的I/O标准设置来定制,简化第三方工具的分析

3、支持双核CPU的嵌入

4、可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;

芯片(电路)平面布局连线编辑

5、LogicLock增量设计方法,用户可建立并优化系统,然后知识兔添加对原始系统的性能影响较小或无影响的后续模块

功能强大的逻辑综合工具

6、完备的电路功能仿真与时序逻辑仿真工具

7、定时/时序分析与关键路径延时分析

8、可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析

9、支持软件源文件的添加和创建,并将它们链接起来生成编程文件

10、使用组合编译方式可一次完成整体设计流程

11、自动定位编译错误

12、高效的期间编程与验证工具

13、可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件

14、能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件

套件下载

一、套件

用户要想完整的使用 ,需要安装相应的套件,需下载的套件:

1.Quartus II 9.1之前的软件自带仿真组件,而之后软件不再包含此组件,因此必须要仿真安装Modelsim

2.Quartus II 9.1之前的软件自带硬件库,不需要额外下载安装,而10.0开始需要额外下载硬件库,另行选择安装

3.Quartus II 11.0之前的软件需要额外下载Nios II 组件若需要上系统,而11.0开始Quartus II 软件自带Nios II组件

4.Quartus II 9.1之前的软件自带SOPC组件,而Quartus 10.0自带SOPC已经Qsys两个组件,但从10.1开始,Quartus II之包含Qsys组件

5.Quartus II 10.1之前软件包括时钟综合器,即Settings中包含TimeQuest Timing Analyzer,知识兔以及Classic Timing Analyzer,但10.1以后的版本只包含了TimeQuset Time Analyzer,因此需要sdc来约束时序

二、组件

1.11.0_quartus_windows.exe :Quartus II 软件

2.11.0_devices_windows.exe :Quartus II 硬件库

3. 11.0_modelsim_ase_windows.exe :Altera Modelsim 仿真软件>

下载仅供下载体验和测试学习,不得商用和正当使用。